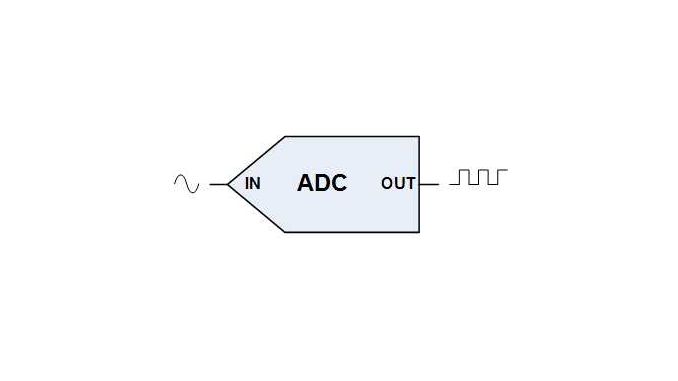

An analog-to-digital converter (ADC) has an analog signal input and transforms it into an integer encoded in a suitable binary code. As in the case of D/A conversion, we can initially assume that the integer is non-negative and the code used is the natural binary.

ADCs do the reverse operation of DACs but with an important difference: while a DAC, beyond the errors due to technological limits, translates exactly the input number into a voltage proportional to it, an ADC cannot translate the input voltage into an exactly proportional integer, because while the input voltage values are infinite and continuous, outgoing integers are not.

In the case of the ADC, a whole range of voltage values is encoded with the same number. With the same range of variation of the input voltage, the more bits are available, the more numbers possible are output, the smaller the intervals in which the field is divided and the higher the resolution.

If we define “quantum” Q the amplitude of the single input voltage range, the relationship between the input voltage Vi and the digital output data Do = (bn–1… b2b1b0) is then the one shown in figure 1.

where ε is the quantization error (or, more exactly, the error in absolute value, being more properly the error ±ε). It represents the uncertainty with which we can reconstruct the analog input voltage Vi from the output numerical data. In fact, the only thing we can deduce from the output, is that the input is “close” to the value Q·Do. The “true” value V differs (more or less) by a non-determinable value that is precisely the quantization error:

Q · D0 – Vi= ± ε

Given the subdivision of the measuring range into amplitude ranges Q, it is clear that the quantization error cannot exceed one quantum, that is, 1 LSB in terms of bits (always unless technological defects). The error ε can be minimized if you choose the quantization intervals so that you have Vi = Q · D exactly at the center of the interval identified by D (fig. 2a): in this case the error is contained in absolute value within half as much as (ε≤ Q/2) and is null at the center of the quantization interval. Figure 2b refers to the extreme case where it is ε = Q.

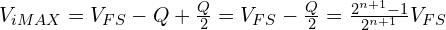

Similar to the case of DACs, even for A/D converters the manufacturers generally do not specify the quantum but the resolution in number n of bits and the full-scale voltage VFS, related to the quantum from the already known relationship:

![]()

The transcharacteristics of an ADC can then be expressed (in the hypotheses of figure 2a) as:

![]() , con

, con ![]()

If, as in figure 3, we report the transcharacteristics of an ADC with n = 3 bits, we can deduce a couple of useful observations.

- The least significant bit (LSB) becomes 1 when Vi reaches (Q/2) = (VFS /2n+1)

- The maximum value for which the quantization error is zero is VFS – Q. Consequently, considering that the output can no longer change, the maximum input value for which the error remains contained in the limit of half quantum, is half quantum after, namely:

To be rigorous, it is this value to which the maximum signal should be conditioned to make the most of the resolution of the ADC; in practice, it is often done on the full scale, and the maximum quantization error at the end of the measuring range thus increases to a quantum (1 LSB).

Note that the first quantization interval is halved, because we have assumed the unipolar ADC (it does not accept negative voltages): here the maximum error is still Q/2, but without the sign uncertainty (it is ε ≤0, because the measured value is 0 while 0 ≤ Vi ≤ Q/2).

Quantization error as noise

The quantization error can be interpreted as a noise that overlaps the original signal. Consider the ideal experiment illustrated in Figure 4: a time-varying Vi analog signal is converted to digital by an ADC and again converted back into a Vo(t) analog signal by a DAC with the same resolution and full scale voltage (and therefore the same quantum) as the ADC.

We neglect the problems related to the acquisition of variable signals in time and conversion time. As we have seen, an instantaneous value Vi is encoded by the ADC in an integer Do bound to Vi by Vi = Q · Do ±ε, with quantization error included in half quantum. In turn, Do is converted by the DAC back to the analog value Vo = Q · Do; the reconstructed signal thus differs from the original one of the quantization error: Vo = Vi ±ε. In other words, in digital processing the original signal is “spoiled” by a noise r = ±ε.

The trend over time, r(t), of this noise depends on that of input vi(t): if Vi(t) is a ramp ranging from 0 V to viMAX, the error varies cyclically and linearly from a minimum of –Q/2 to a maximum of Q/2, canceling out when the input is an exact multiple of a quantum. In other words, r(t) noise is an alternating sawtooth signal of peak values:

![]()

and rms value:

![]()

In the example of figure 5, with a full scale of 5 V and 3 bits of resolution, the quantum is Q = 5/8 = 6.25 V, and coincides, in coherence with the relationship seen, with the peak-to-peak amplitude of the quantization noise.

In the characterization of an ADC, the signal-to-noise ratio assumes a particular value:

![]()

where Pi/Pr=V2ieff/V2reff is the ratio between the powers (referring to a unit resistive load) of the signal and the noise (here assumed as deriving from the quantization error alone).

To evaluate this ratio, an alternating sinusoid is assumed as input that varies from: ![]() a

a ![]() that is, of rms value

that is, of rms value ![]()

We then assumed that the ADC has bipolar input or that the signal is “moved up” by an offset equal to its peak value. In the latter case, the contribution to the effective value of the continuous component of the offset, which does not carry information, is neglected.

Assuming, as mentioned, that the noise remains approximately a sawtooth:

and then:

![]()

That is, every bit of extra resolution makes it gain on quantization noise. Figure 6 shows the comparison between this theoretical relationship and the value of the actual signal-to-noise ratio as shown by a simulation. As you can see the approximation is good, especially for resolutions not too low. It can be shown that the relationship found also works well for other types of signals (square, triangular, sawtooth wave, etc.).

In the event that the signal does not cover the entire input variation range of the ADC, the signal-to-noise ratio is lower, and it can be shown that for a peak-to-peak sine wave ViPP is:

![]()

Because 20log(ViPP/VFS )< 0 for ViPP< VFS, the signal-to-noise ratio worsens (logarithmically) as the signal amplitude decreases.

To overcome the worsening of S/N on weak signals, non-linear scale ADCs are often used in digital telecommunications, which expand the low levels by reserving them a greater number of bits.